MINISTRY OF EDUCATION AND SCIENCE OF UKRAINE

NATIONAL TECHNICAL UNIVERSITY «KHARKIV POLYTECHNIC INSTITUTE»

# ELECTRONICS AND MICROPROCESSOR TECHNOLOGY

LABORATORY MANUAL ON ELECTRICAL ENGINEERING Part III

Kharkiv 2024

### EDUCATION AND SCIENCE MINISTRY OF UKRAINE

## NATIONAL TECHNICAL UNIVERSITY «KHARKIV POLYTECHNIC INSTITUTE»

## DEPARTMENT OF APPLIED ELETRICAL ENGINEERING

Volodymyr Boliukh , Vladyslav Markov, Euhen Honcharov, Ihor Poliakov, Natalia Kriukova, Yuriy Kashansky

# ELECTRONICS AND MICROPROCESSOR TECHNOLOGY LABORATORY MANUAL ON ELECTRICAL ENGINEERING

In three parts Part III

> Approved by the editorial and publishing council of NTU "KhPI", protocol № 2 from 27<sup>th</sup> June 2024

Kharkiv NTU KhPI 2024 **Reviewers:**

Oleksandr Sereda, Doctor of Engineering, professor, National Technical University «Kharkiv Polytechnic Institute» Victor Kharchenko, Doctor of Engineering, professor, Kharkiv National University of Municipal Services named after O. Beketov

E 50 Electronics and microprocessor technology: laboratory manual on electrical engineering. In three parts. P. III / V.F. Boliukh, V.S. Markov, E.V. Honcharov and others. – Kharkiv: NTU "KhPI", 2024. – 96 p.

The course of five laboratory works from the section "Electronics and microprocessor technology" of the discipline "Electrical engineering, electronics and microprocessor technology" has been presented in the form of a complex independent work for preparation for the execution of these laboratory works. Theoretical material on the design and principle of operation of devices, as well as the methodology for their calculation, are provided. The laboratory manual has been intended for independent work of students in the preparation and execution of laboratory, calculation and graphic works, preparation for tests and exams. Part I was published in 2022, Part II was published in 2023.

Іл. 73. Табл. 23. Бібліогр. 11 назв.

УДК 621.3.011.7

© Boliukh V.F., Markov V.S., Honcharov E.V., Polyakov I.V., Kriukova N.V., Kashansky Y.V., © NTU "KhPI", 2024

#### **INTRODUCTION**

The proposed laboratory works are component of the educational process and intended for full-time, part-time and distance learning students.

It involves the consistent acquisition of knowledge related to the study and calculation of electronic devices.

The purpose of laboratory classes is to consolidate theoretical knowledge and acquire practical skills in drawing up electric circuits and turning on different electronic devices, measuring currents and voltages.

On the basis of these studies, calculations of electronic devices are carried out, as well as analysis of research results.

In the laboratory workshop, the safety rules for performing laboratory works, the procedure for their implementation, theoretical provisions, the design and content of the report, and the diagrams for connecting electronic devices and devices are given.

## DESCRIPTION OF THE UNIVERSAL LABORATORY BENCH FOR PERFORMING A LABORATORY WORK ON ELECTRONICS

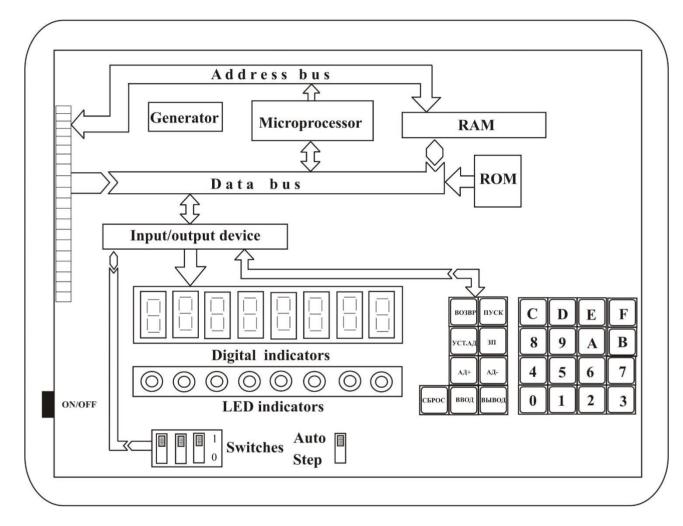

The K4824 universal laboratory bench was intended for carrying out laboratory works from the section "Electronics and microprocessor technology" using the frontal method. The bench is contained in a portable case with a hinged top cover. It is powered by a single-phase AC source of 220 V, 50 Hz. Connecting to the source is done using an electric cord with a standard two-pole plug.

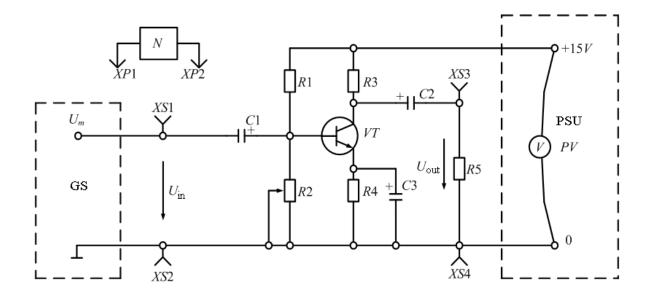

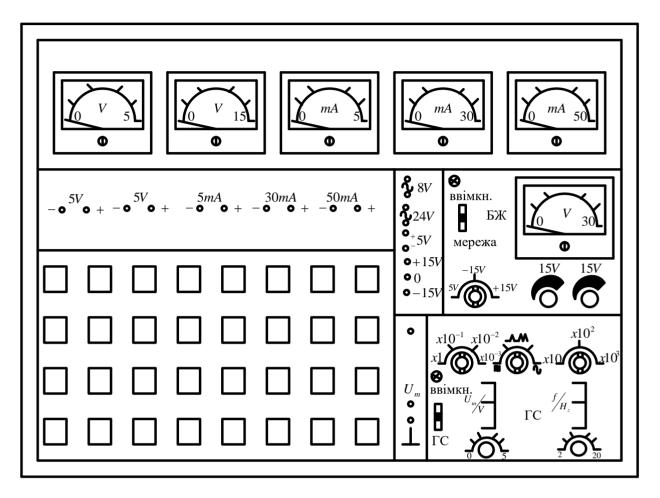

The working field of the bench is shown in Fig. 1. It is divided into the following zones: the power supply unit (PSU – « $\mbox{GW} \mbox{"}$ ) in Fig. 1), the signal generator panel (SGP – « $\mbox{C} \mbox{"}$ ) in Fig. 1), the mounting panel and the panel with electric measuring devices. On the panels of the power supply unit and the generator there are control bodies, indications and sockets for the PSU and SGP outputs. Toggle switch "network-on" (« $\mbox{"BBIMKH}$ . Mepe $\mbox{max"}$ ) in Fig. 1), placed on the power supply unit, voltage is applied (the light indicator lights up) to the power supply unit. Across its terminals "~ 8 V"; "~ 24 V" appears alternating voltages of 8 V and 24 V with a frequency of 50 Hz; across terminals "5 V" - direct stabilized unregulated voltage of 5 V; across the terminals "+ 15 V" and "- 15 V" relative to the common output "0" – regulated voltages from 5 V to the specified maximum values of + 15 V and - 15 V (the control knobs "+ 15 V" and "- 15 V" are intended specifically for this).

The voltmeter, located on the PSU panel, can be connected with the handle "+5V; -15V; +15V" to the corresponding sources of constant voltage for its control.

The limit values of the current supplied to the load by any of the sources of the power supply unit should not exceed 0,1 A!!!

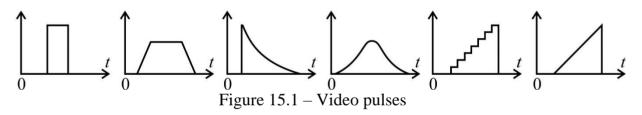

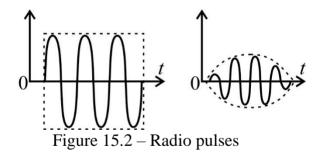

The SGP produces voltages of various forms, which are applied to the terminals  $\ll U_m \gg$  and  $\ll \perp \gg$ . This generator is turned on by the "SGP-on" toggle switch, while the corresponding light indicator lights up. The selection of the voltage form of

the SGP signal is carried out with a handle, next to which the voltage forms generated by it are depicted (rectangular, triangular, sawtooth, sinusoidal).

Figure 1 – Universal laboratory bench K4824

The magnitude of the output voltage of the signal is regulated by the knobs marked " $U_m$  / V" (stepwise and smoothly within the range of 0...5 V), and the frequency of the signal - by the knobs marked "f / Hz" (stepwise and smoothly within the range of 20...20000 Hz).

The signal parameters set by the knobs are approximate, their values must be determined by appropriate measuring devices.

Two voltmeters and three milliammeters of the magnetoelectric system are fixed on the panel of electric measuring devices, which can measure constant or rms values of quantities. This panel can be installed at an angle of 0...30° relative to the surface of the bench body (for convenience of measurements).

Observation of the form of variable signals and measurement of their parameters is carried out with the help of electric measuring devices that are not included in the bench (oscilloscopes, electronic voltmeters).

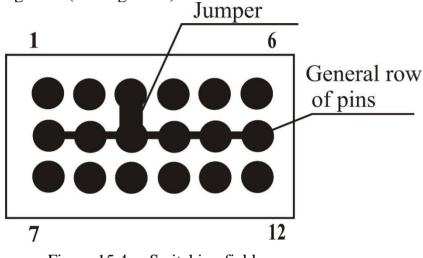

The mounting field, which occupies most of the panel of the bench, contains mounting sockets connected by four to each other. Each such group is an electrical node that allows you to connect up to four elements. Electric elements and semiconductor devices (resistors, capacitors, diodes, thyristors, transistors, etc.) are contained in transparent plastic boxes with electric terminals, which have inscriptions with information about the type of element and its parameters. They can be connected to each other directly at nodes or using conductors with plug contacts.

## SAFETY TECHNIQUES DURING IMPLEMENTATION A LABORATORY WORK

Laboratory benches are active electric circuits and electrotechnical devices, which under certain conditions can become sources of electric shock. In order to create safe working conditions in the laboratory and prevent the possibility of damage to electric equipment, students must know and strictly follow the following rules:

1. Before starting work, make sure that all power sources are in the "OFF" position, and the slider of the autotransformer is set to the zero position.

2. It is strictly forbidden to touch uninsulated wires, connecting clamps and other live parts of electric circuits.

3. Assembling of the electric circuit of the electric device and any connections must be made with the power sources turned off.

4. It is strictly forbidden to turn on the laboratory bench without checking the electric circuit by the tutor.

5. If the network voltage disappears during operation, you should immediately turn off the laboratory bench and set the slider of the autotransformer to the position corresponding to the minimum voltage.

6. Disassemble the circuit only with the permission of the class tutor.

7. If any malfunction is detected in an electric device that is under voltage, it is necessary to turn off the test bench from the network immediately using the emergency shutdown button. This case should be reported to the class tutor immediately.

## THE PROCEDURE FOR PERFORMING A LABORATORY WORK

To perform the work, academic groups of students are divided into subgroups of 2 - 4 students. Laboratory work is carried out by the frontal method, that is, all subgroups simultaneously perform the same work, but at different laboratory benches.

To perform laboratory work, each student should prepare a test protocol (draft) in advance, which contains an electric circuit of the experiment and a table of measurements. Before starting the experiments, the subgroup should get acquainted at the workplace with the experimental installation, power sources, electric loads and devices that are used.

During the assembly of the circuit, it is recommended to assemble the main electric current circuit with the inclusion of the receivers to be investigated and the current circuits of ammeters, wattmeters and phasometers. Then you can connect circuits of voltmeters, wattmeters and phasometers, which are turned on in parallel with the loads. It is necessary to remember the rule that the terminals of devices are used only for their inclusion in the circuit. Nothing else is connected to these terminals, and all additional connections are made to free terminals on the bench panel.

The completed circuit must be shown for verification; power sources should be switched on only with the tutor's permission.

The results of all primary measurements and calculations are recorded in previously prepared tables.

At the end of the experiment, the power sources are turned off, and the measurement results are submitted to the class leader for verification.

If the results of the experiment are recognized by the tutor as correct, the electric circuit is disassembled and the next circuit is drawn up. After the research is completed, the workplace is organized, the conductors and devices are handed over to the place of their storage.

## FORMATION AND CONTENTS OF THE REPORT ON A LABORATORY WORK PERFORMED

The report on laboratory work is written by each student separately and must be neat, completed in accordance with the established form.

The report begins with a title page, a sample of which is given on page 7. On the following pages, it is necessary to indicate:

- electric circuits of the experiment;

- rated data of devices under investigation, necessary for writing the report;

- formulae and dependencies used for calculations;

- tables of measurement data and calculation results in accordance with the requirements specified in the methodical instructions for each laboratory work;

- graphic material (graphs, diagrams, drawings);

- analysis results and work conclusions.

Schematic diagrams are drawn using tools according to DSTU (The Ukrainian Standard). Conventional values of typical elements and their sizes are given in the Table 1. It is advisable to build graphs of dependencies obtained on graph paper with standard letter designations of values and measurement units on the axes.

Phasor diagrams must be drawn at the selected scale.

The report is accepted by the lecturer on the day when the next work is performed. At the same time, the student must analyze the obtained results, answer control questions and solve problems according to the topic of the work.

| Ministry of Education and Science of Ukraine                                              |

|-------------------------------------------------------------------------------------------|

| National Technical University<br>«Kharkiv Polytechnic Institute»                          |

| Department of Applied Electrical Engineering                                              |

| Report on laboratory work №                                                               |

| (the title of the work)                                                                   |

| Work was performed by:<br>student; group;<br>(surname, initials) (index) (execution date) |

| The report was accepted onLecturer(date) (position, surname, initials)                    |

| Kharkiv                                                                                   |

| (Year)                                                                                    |

| Title of elements                                                                               | 5                                                | Designation on a schematic diagram <i>я</i> | Dimensions, mm                  |  |  |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------------------------|---------------------------------|--|--|

| Resistor                                                                                        | constant<br>resistance<br>variable<br>resistance |                                             |                                 |  |  |

| Capacitor of constant a capacitance                                                             | and variable                                     | $\frac{1}{1} \frac{1}{7} \frac{1}{7}$       |                                 |  |  |

| Inductive element, inductance<br>Inductor (air-core coil)<br>Inductor (iron-core coil)          |                                                  |                                             | <u>R 1,54</u>                   |  |  |

| Adjustable autotransformer                                                                      |                                                  | <b>اً ب</b> ∎ ۲۱<br>۲ <b>س</b>              | Å                               |  |  |

| Single-phase semiconduc<br>rectifier                                                            | tor bridge                                       |                                             |                                 |  |  |

| Electric meters:<br>PA – ammeter; $PV$ – voltmet<br>$PW$ – wattmeter; $P_{\phi}$ – phase        |                                                  |                                             | Ø10                             |  |  |

| Joints                                                                                          | separable<br>non-<br>separable                   | XT                                          | <u>Ø1,52</u>                    |  |  |

| Contacts of detachable conn<br>(male connector $-XP$ and<br>female connector $-XS$ )            | ection                                           | $\xrightarrow{XP}$                          | <u>900</u> <u>23</u>            |  |  |

| Contacts of switching<br>equipment<br>(Q - in the power circuits;<br>S - control, alarm system) | make<br>break                                    |                                             | <u>6</u> <u>30</u> <sup>0</sup> |  |  |

| Current                                                                                         | direct<br>alternating                            | ー<br>~                                      |                                 |  |  |

## Table 1 – Legend of functional elements in electric circuits

## Continuing of Table 1

| Title of elements                       | Designation a schematic diagram | Dimensions, mm       |

|-----------------------------------------|---------------------------------|----------------------|

| Single-phase double-winding transformer |                                 | <u><i>R</i> 1,54</u> |

| Diode                                   |                                 |                      |

| Zener diode                             |                                 |                      |

| Thyristor (dynistor)                    |                                 |                      |

| Transistor ( <i>n-p-n</i> type)         |                                 |                      |

| Measuring oscilloscope                  | N                               |                      |

#### Laboratory work 11

## **RESEARCH OF SEMI-CONDUCTOR RECTIFER DIODE,** ZENER DIODE AND DYNISTOR

#### **11.1. Purpose of the work**

The purpose of the work is to study the design and operation principle of the semi-conductor rectifier diode, Zener diode (stabilitron) and dynistor (uncontrolled thyristor), as well as the experimental study of the current-voltage characteristics (CVC) of these devices.

#### **11.2.** Theoretical provisions

The main physical processes in semiconductor devices are the generation of charge carriers, control of their concentration and movement. These processes are formed with the help of electrophysical properties of semiconductor materials that are part of all semiconductor devices.

Germanium Ge, silicon Si, selenium Se, as well as semiconductor compounds such as gallium arsenide, silicon carbide, cadmium sulfide, etc., are most widely used in semiconductor technology.

Charge carriers in semiconductors are electrons and holes. Accordingly, electron and hole conductivity are distinguished. The formation (generation) of a pair of charge carriers (electron-hole) in a semiconductor occurs under the influence of external factors, such as an increase in temperature, the action of an external electric field and light, etc.

The concentration of electron-hole pairs in a semiconductor is determined by the balance between the processes of generation of pairs and their recombination (inconnection of pairs). Such a concentration forms the intrinsic electric conductivity of the semiconductor, which increases as the action of external factors increases.

Under normal conditions, the intrinsic electric conductivity of semiconductors is quite small compared to the electric conductivity of conductors. So, for example, 1 cm<sup>3</sup> of pure germanium at room temperature contains  $2,5 \cdot 10^{13}$  pairs of electron-holes with a total number of atoms of  $4,2 \cdot 10^{22}$ , while 1 cm<sup>3</sup> of the metal contains  $10^{22}-10^{23}$  atoms and the same number of charge carriers (electrons).

Impurities are used to increase the electric conductivity of semiconductors. Materials of the third group of Mendeleev's periodic table of elements (gallium Ga, indium In) or the fifth group (antimony Sb, phosphorus P) are used as impurities. The addition of a small  $(10^{-5}-10^{-6} \%)$  but precisely set amount of impurities to a pure semiconductor ensures a multiple  $(10^{3}-10^{5} \text{ times})$  increase in additional carriers compared to the charges related to the conductor's own electric conductivity. At the same time, the impurity gives the semiconductor a sharply pronounced character of electron or hole conductivity. Electron impurity conductivity occurs in a

semiconductor when the impurity has one more valence electron than the semiconductor. In this case, the semiconductor is called an N-type semiconductor, and the impurity is called a donor.

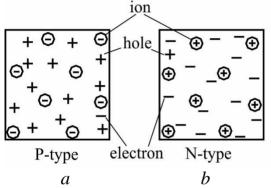

Hole impurity electric conductivity occurs in a semiconductor when the impurity has one valence electron less than the semiconductor. In this case, the semiconductor is called a P-type semiconductor, and the impurity is called an acceptor. Along with the charge carriers formed in the semiconductor, immobile positive ions appear in the N-type semiconductor (Fig. 11.1, a) and negative ions in the P-type semiconductor (Fig. 11.1, b).

Figure 11.1 – Designation of stationary and mobile charge carriers

Charge carriers in a semiconductor caused by an impurity are called main carriers. In N-type semiconductors, these are electrons, and in P-type semiconductors, they are holes. However, along with the main charge carriers in semiconductors, there are a small number of non-main charge carriers, which are formed by thermogeneration (under the influence of heat) of electron-hole pairs and determine their own electric conductivity.

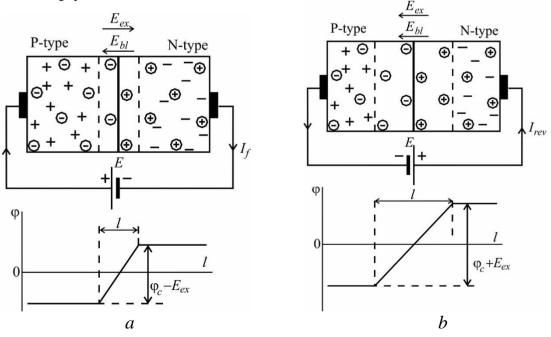

**11.2.1. Properties of** p-n **junction.** The principle of operation of most semiconductor devices is based on specific phenomena that occur at the interface between N- and P-type semiconductors, where an electron-hole or p-n junction is formed in the adjacent thin layer. The type of semiconductor is determined by its main charge carriers caused by the presence of an impurity. An N-type semiconductor contains electrons, and a P-type semiconductor contains holes. Let's consider these phenomena using Fig. 11.2.

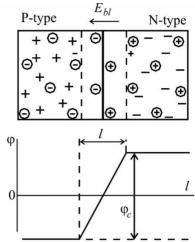

Due to the different concentration of the main charge carriers on both sides of the semiconductor interface, a part of the holes from the boundary region of the P-type semiconductor diffuses (penetrates) into the N-type semiconductor, and a part of the electrons from the boundary region of the N-type semiconductor diffuses into the P-type semiconductor. As a result, a layer of immobile ions is formed along the boundary of the distribution of semiconductors, in which there are no mobile charge carriers, and as a result, such a barrier layer has a high electric resistance. The thickness of the barrier layer *l* usually does not exceed several microns (Fig. 11.2).

The expansion of the barrier layer is hindered by immobile ions of impurities that form an electric double layer. This layer determines the contact potential difference  $\Delta \varphi$  (potential barrier) at the boundary of semiconductors, which is, of

course, 0.3 - 0.5 V. The potential difference creates an electric field with a blocking EMF  $E_{bl}$  in the barrier layer, which prevents the passage of the main charge carriers through the *p*-*n* junction and does not prevent the passage of non-main charge carriers through it.

Figure 11.2 – To physical processes in a p-n junction

Upon reaching a certain value of  $E_{bl}$ , a dynamic equilibrium occurs, in which the strength of the diffusion current  $I_f$ , caused by the diffusion of the main charge carriers, becomes equal to the strength of the reverse (drift) current  $I_{rev}$ , caused by the movement of non-main charge carriers under the influence of the electric field  $E_{bl}$ .

When an EMF source *E* is connected to the *p*-*n* junction (Fig. 11.3, *a*) in the forward direction ("+" of the source to the P-type region and "-" of the source to the N-type region), the external electric field of the source  $E_{ex}$  weakens the field  $E_{bl}$ , reduces potential barrier to  $\Delta \varphi' = \varphi_c - E_{ex}$  and reduces the thickness of the barrier layer *l*. As a result, the diffusion and with it the current through the *p*-*n* junction increases sharply.

Figure 11.3 – Forward and reverse connection of a *p*-*n* junction

With the reverse connection of the EMF source to the *p*-*n* junction (Fig. 11.3, *b*), the external field  $E_{ex}$  coincides in direction with the field  $E_{bl}$  and thereby contributes to the expansion of the barrier layer to *l* and the increase of the potential barrier to  $\Delta \varphi'' = \varphi_c + E_{ex}$ . At the same time, the resistance of the *p*-*n* junction increases sharply, and the current practically does not pass through this junction. Therefore, the *p*-*n* junction has one-way conductivity, which is practically used in a whole range of semiconductor devices - diodes, transistors, thyristors, etc.

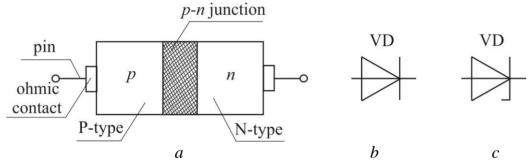

**11.2.2. Semiconductor diode.** A semiconductor diode is a semiconductor device with one p-n junction and two terminals, which uses the property of the p-n junction to conduct current well in one direction and poorly in the opposite direction. Diodes designed to convert an alternating current into a direct current are called rectifiers. The structure, conventional designations of the diode and Zener diode are shown in Fig. 11.4, a, b, c.

Figure 11.4 – Structure and designations of a rectifier diode and a Zener diode

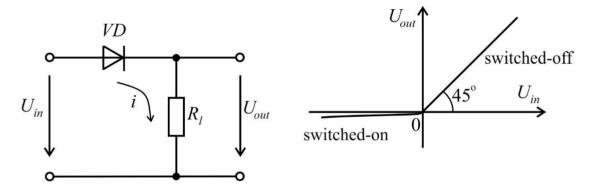

The properties of a semiconductor diode are determined by the non-linear current-voltage characteristic (CVC) of the open and closed junction (Fig. 11.5).

When the diode is switched on in forward direction, the positive pole of the direct voltage source is connected to the terminal of the P-type semiconductor. and the negative pole is the terminal of the N-type connected to semiconductor. The reverse is the case when it is switched back on. On the sections 1 and 2 of CVC correspond to forward switching of the diode, and sections 3 and 4 to reverse switching. With forward switching, the electric field of the p-n junction and the source of constant voltage are directed toward each other, and with reverse switching, they coincide.

In section 1, the electric field of the p-n junction is greater than the electric field of the source and, accordingly, the direct current is

rectifier diode

insignificant. In section 2, the external field of the source is greater than the blocking field of the p-n junction, there is no blocking layer, the current is determined only by

the resistance of the semiconductor. This resistance is relatively small, which leads to a slight voltage drop at the *p*-*n* junction ( $U_f \leq 1,2$  V). The forward current is a diffusion current.

In section 3, the blocking layer of the p-n junction prevents the movement of the main carriers. The resistance of the closed p-n junction is relatively large, and the external voltage of the source falls entirely on it. A small current determines the movement of non-basic charge carriers (electrons of a P-type semiconductor and Ntype holes). This reverse current is called a drift current. It is due to the fact that for a number of non-basic carriers, the blocking field creates a force and acceleration sufficient to overcome the *p*-*n* junction. In section 4, a *breakdown* of the *p*-*n* junction occurs and the reverse current increases rapidly. This is due to the fact that when moving through a *p-n* junction under the influence of an electric field, non-main charge carriers acquire energy sufficient for impact ionization of semiconductor atoms. In the transition, the avalanche multiplication of charge carriers begins. This type of *electric breakdown* is called an *avalanche*. It develops in lightly doped semiconductors with a relatively wide *p*-*n* junction. In heavily doped semiconductors, the width of the p-n junction is relatively small, which prevents the occurrence of an avalanche breakdown due to insufficient energy for impact ionization, acquired by moving carriers. In this case, an electric breakdown of the *p*-*n* junction may occur.

If the temperature of the p-n junction increases as a result of its heating by current and insufficient heat dissipation, then the generation of pairs of charge carriers increases, which leads to a further increase in the reverse current, heating of the p-n junction and can cause its destruction. Such a process destroys the p-n junction and is called a thermal breakdown.

The limitation of the value of the forward current  $I_f$  is due to the thermal destruction of the diode, and the value of the reverse voltage  $U_{rev}$  is due to thermal breakdown and the destruction of the rectifying properties of the diode. Both of these quantities are the main parameters of diodes.

According to the design of the *p*-*n* junction, semiconductor diodes are divided into point and planar. A point diode is a device with a very small area of electric transition, which can be obtained by fusing a metal needle with an impurity applied to it into a semiconductor plate with a certain type of electric conductivity. At the same time, impurities diffuse from the needle into the main semiconductor, which create an area with a different type of electric conductivity. Thus, a miniature *p*-*n* junction is created near the needle. Due to the small area of the *p*-*n* junction, the point diode belongs to low-power devices. The permissible dissipation power of this type of diode is of the order of 10 mW at a value of the forward current of the diode of 10 - 20 mA.

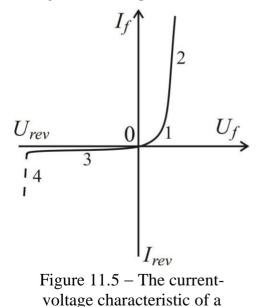

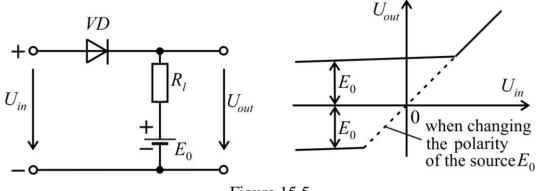

**11.2.3. Semiconductor Zener diode.** Semiconductor Zener diode (planar diode, stabilitron) is a semiconductor diode, the voltage on which in the area of *electric breakd*own depends weakly on the current strength and which is used to stabilize the voltage.

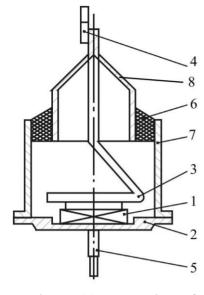

Zener diodes are manufactured as silicon planar diodes. Planar diodes and Zener diodes are devices with a significant area of the p-n junction obtained by fusing

semiconductor plates with different types of charge carriers or diffusion of impurity atoms into the original semiconductor plate. In Fig. 11.6 shows the design of a Zener diode. The semiconductor crystal plate 1 is soldered to the crystal holder 2, so that a contact is formed. Outputs 4 and 5 are made from this contact and electrode 3, and the upper output 4 passes through the glass pass-through insulator 6 into the housing 7 and the tube 8.

Flat diodes of low dissipation power  $(P = 1 \text{ W}, I_f \le 1 \text{ A})$  are used in automation and instrument engineering. High-power diodes  $(P = 10 \text{ kW}, I_f \le 2 \text{ kA})$  are used mainly in rectifiers.

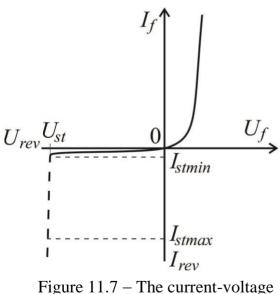

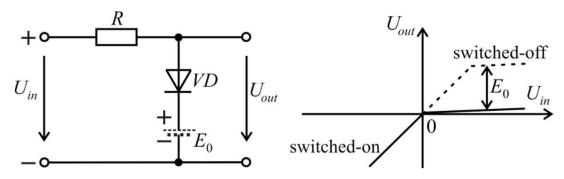

The phenomenon of *electric breakdown*, which is dangerous for ordinary diodes, finds a useful application in silicon planar diodes, which have received the name of silicon zener diodes or reference diodes. The CVC of the Zener diode is shown in Fig. 11.7.

The normal mode of operation of Zener diodes is operation when the *p*-*n* junction is reversed. The stabilization section is located on the CVC of the stabilizer from  $I_{st.min}$  to  $I_{st.max}$ . The value of the minimum

stabilization current is limited by the non-linear section of the reverse part of the CVC of the Zener diode. The value of the maximum stabilization current is the permissible temperature of the semiconductor. In the area of stabilization, the voltage drop across the Zener diode practically does not change, which allows you to use the device as a voltage stabilizer.

The direct current circuit of the zener diode is similar to the corresponding current circuit of the diode.

The main parameters of the Zener diode:

1) stabilization voltage  $U_{st}$  – the voltage drop across the Zener diode in the stabilization area at a normal value of the current;

2) the minimum stabilization current  $I_{st.min}$  is the value of the current through the stabilizer diode, at which a stable *avalanche breakdown* occurs;

3) maximum stabilization current  $I_{st.max}$  – the largest value of the current through the zener diode, at which the dissipation power across the Zener diode does not exceed the permissible value;

Figure 11.6 – Design of a Zener diode

characteristic of a Zener diode

4) differential resistance  $R_{dif}$  in the area of stabilization, which characterizes the degree of voltage stability when the current changes in the area of the avalanche breakdown;

5) the maximum dissipation power  $P_{\text{max}}$  is the largest power released in the *p*-*n* junction, at which the thermal breakdown of the *p*-*n* junction does not occur.

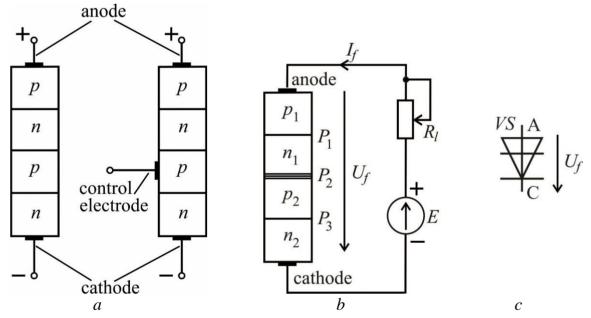

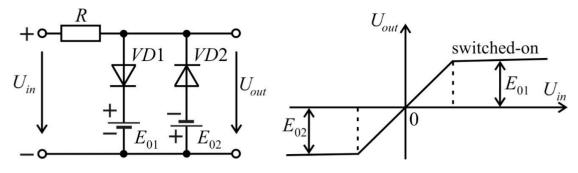

**11.2.4. Semiconductor thyristor (dynistor)**. A thyristor is a conductor device with two stable states, which has three (or more) p-n junctions and can be switched from a closed state at the same time.

Thyristors with two terminals are called single or dynistors (uncontrolled thyristors), and with three-terminal or treenistors (controlled thyristors).

Fig. 11.8 *a*, *b* shows the structure of a threenistor and a dynistor, and also the designation of a dynistor. The control electrode in a threenistor is called a gate. The structure consists of four sections of the conductor with electric conductivity types  $p_1$ - $n_1$ - $p_2$ - $n_2$ , which are combined and between, which three electron cores are created,

the P1, P2, P3 junctions are situated.

Figure 11.8 – A stuctural diagram of a threenistor (a), a dynistor (b) and designation of a dynistor

The outer layers of the thyristor  $p_1$  and  $n_2$  are made with low resistance (with a large number of impurities), as a result of which they are enriched with the main carriers of charges, and the internal layers  $p_2$  and  $n_1$  are made with high resistance (with a small number impurities), that they are imbued with similar charge carriers. When switched on in the forward direction, the voltage is supplied to the thyristor in such a way that junctions P1 and P3 are switched on in the forward direction, and junction P2 is switched on in the reverse direction. Therefore, the maximum voltage U drops across the closed junction P2. Apparently, the thyristor closes and passes a small flow at the P2 junction, which creates a non-main charge carrier.

With an increased voltage U that is applied to the thyristor (which is within the reach of larger EMF of the source), the flow of the thyristor increases

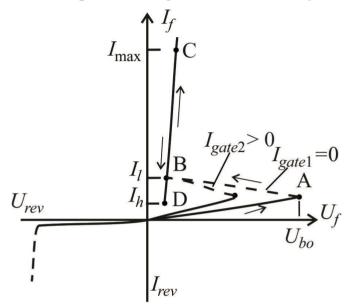

significantly, so that the thyristor behaves as a voltage under the return voltage. This is shown on the current-voltage characteristic by section 1 (Fig. 11.9).

While the thyristor is closed, the electric field of the external voltage appears on the charge in the P2 junction, but the stronger electric field at the thin sphere of the *p*-*n* junction increases the fluidity of the flow of electrons and have a nice run. When the voltage reaches a critical value of the forward voltage or the breakdown voltage  $U_{bo}$  which brings the thyristor CVC to the point **A** (Fig. 11.9), the fluidity of

the charge becomes sufficient for the alignment of the valence bonds of the atoms on the conductor. There is an avalanche-like increase in the number of charge carriers and ionization of the P2 junction; the internal layers of the thyristor carry a charge from the external lowimpedance layers. The current grows sharply and is surrounded only by the load resistor  $R_l$ . The voltage across the  $R_l$  increases, and across the thyristor decreases. Therefore, the differential operation  $R_{dif}$  will be negative. This mode of the thyristor is unstable and demonstrates part

Figure 11.9 – The current-voltage characteristic of a dynistor

between points **A** and **B** on the CVC (dash line in Fig.11.9). The thyristor spontaneously switches on to "On-state" position (point **B**). After a breakdown, the voltage on the thyristor drops to 0.5 - 1 V, therefore, an avalanche breakdown at low voltage and high flow does not cause irreversible processes in the thyristor structure.

The point **B** is characterized by the latching current. It is minimum forward current required to maintain a thyristor in the "On-state" immediately after switching from the "Off-state" to the "On-state" has occurred and the triggering signal has been removed.

With a further increase in the voltage of the power source *E* or the changed load  $R_l$  current of the thyristor continues to increase, the voltage across the new one changes slightly, which indicates part **BC** of the thyristor CVC. At this part, the static resistance of the thyristor  $R_{st} = U/I$  is small.

The point **C** is the maximum current in "On-state". The point **D** is the holding current minimum current required to maintain a thyristor in the "On-state" position. If we have threenistor or controlled thyristor, then the bigger value of the current of the gate  $I_{\text{gate}}$  (control electrode), the lower value of the breakdown voltage we have and the faster the thyristor appears in "On-state".

When the thyristor is reversely connected, the dynistor is in a closed state, so junctions P1 and P3 are located in the non-conductive direction. There is a reverse voltage between them and therefore no breakdown is detected. The static resistance

of the thyristor at this stage of the CVC is large. To overcome the breakdown of the thyristor, which fails the thyristor due to possible thermal breakdown, it is necessary that the reverse voltage value should be less than the maximum allowed value.

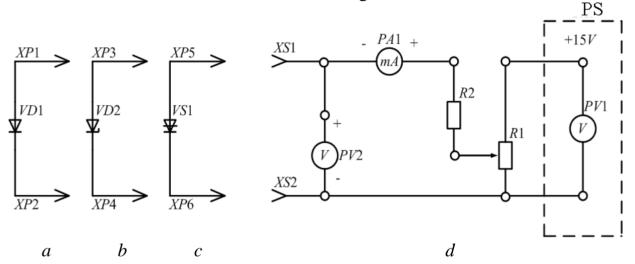

#### 11.3. Object of study

The schematic diagram of the experiment electric circuit is shown in Fig. 11.10. Rectifier diode VD1, Zener diode VD2 and VS1 dynistor, which are dualelectrode semiconductor devices, are shown, respectively, in Fig. 11.1, *a*, *b*, *c*; power circuit and measurement devices are shown in Fig. 11.1, *d*.

Figure 11.10 – The shematic diagram of the experiment electric circuit

The power supply (PS) is equipped with a voltmeter voltage regulator 15 or 30 volts. The power supply voltage is measured by a *PV*1 voltmeter. Adjusting the voltage can be done by the additional resistor  $R_1$  (2,2 kOhm), which is switched on as the potentiometer circuit is used to limit the current, the ballast resistor  $R_2$  (300 Ohm). The *PA*1 mini ammeter and *PV*1 voltmeter are used for measurement current and voltage across diodes. The devices will be connected to XS1 and XS2 sockets by XS1 and XS2 pins in forward direction.

Each device should be switched on two times: first – as shown in Fig. 11.1, the other in reverse direction for this it's enough to turn on a device by 180 degrees, i.e. swap its pins.

The main parameters of the considered devices are given in Table 11.1, 11.2 and 11.3.

| Type of the | Forward    | Forward DC | Reverse maximum           | Direct reverse             |

|-------------|------------|------------|---------------------------|----------------------------|

| rectifer    | current, A | voltage, V | voltage $U_{rev.max}$ , V | current at $I_{rev.max}$ , |

| diode       |            |            |                           | mA                         |

| КД209А      | 0,1        | 1,0        | 400                       | 0,1                        |

Table 11.1

Table 11.2

| Type of | Stabilization       | Minimal        | Maximal        | Direct   | Differential |

|---------|---------------------|----------------|----------------|----------|--------------|

| the     | voltage             | current of     | current of     | maximum  | resistance,  |

| Zener   | $U_{\rm st},{ m V}$ | stabilization, | stabilization, | current, | Ohm          |

| diode   |                     | mA             | mA             | mA       |              |

| Д814А   | 78,5                | 3              | 40             | 50       | 6            |

#### Table 11.3

Table 11 4

| Name of the dynistor parameters type KH102Γ                                         | Parameters value |

|-------------------------------------------------------------------------------------|------------------|

| Limited forward current in the on-state condition $I_{fmax}$ , mA                   | 200              |

| Forward voltage in the on-state condition at $I_{fmax}$ , $U_f$ , V                 | 1,5              |

| Minimum current in the on-state condition <i>I</i> <sub>fmin</sub> , mA             | 15               |

| Constant maximum direct voltage in the off-state condition $U_{c.s.max}$ , V        | 14               |

| Constant current in the off-state condition at $U_{c.s.max}$ , $I_{c.s.}$ , $\mu A$ | 80               |

| Maximum constant reverse voltage $U_{rev.max}$ , V                                  | 10               |

| Reverse current at $U_{\text{rev.max}}$ , $I_{\text{rev}}$ , mA                     | 0,5              |

#### **11.4.** The order of the experiment execution

Before the assemble of the circuit, it is necessary to connect the laboratory bench to the network, turn on the "network-on" toggle switch, and set the minimum value of the power supply to the voltmeter PV1 of the bench. Turn off the toggle switch. Assemble of the circuit in accordance with Fig. 11.10, d and set the minimum value of voltage at the output of potentiometer R1 by voltmeter PV2.

**11.4.1. Research of a rectifer diode.** Connect the rectifier diode VD1 in the forward direction (Fig. 11.10, a, d).

By changing the current from zero to the maximum value using the potentiometer R1 and the regulator of the power supply unit, read the forward branch of the CVC of the diode  $I_f(U_f)$  (7-8 points). The values of current  $I_f$  and voltage  $U_f$  must be written down in Table 11.4.

A sample of the CVC of the rectifier diode is shown in Fig. 11.5.

| 1 u                       |   |   |  |  |  |

|---------------------------|---|---|--|--|--|

| $U_f$ , V                 | 0 |   |  |  |  |

| <i>I<sub>f</sub></i> , mA | 0 |   |  |  |  |

| $U_{\rm rev}, V$          |   | 0 |  |  |  |

| $I_{\rm rev}$ , mA        |   | 0 |  |  |  |

Turn off the voltage and reverse the diode. To carry out the read of the reverse branch of the CVC named  $I_{rev}$  ( $U_{rev}$ ), changing the voltage from zero to the maximum possible value (it is enough 3-4 points). Write down the results of the measurements in Table 11.4.

**11.4.2. Research of a Zener diode.** Instead of the rectifier diode, connect the VD2 Zener diode to the circuit (Fig. 11.10, b, d).

In this experiment it is necessary to take into account that on the reverse branch of the CVC suddenly arises and the current stabilizes rapidly, while the voltage changes very slowly (the working part of the CVC of the Zener diode). A sample of the CVC of a Zener diode is shown in Fig. 11.7.

Make characterization of the Zener diode CVC in the same way as for the rectifier diode, but with reverse switching it is already necessary to read 6-7 points. Write down the results in the Table 11.5.

Table 11.5

| $U_{f}, \mathbf{V}$          | 0 |  |  |  |  |

|------------------------------|---|--|--|--|--|

| <i>I<sub>f</sub></i> , mA    | 0 |  |  |  |  |

| $U_{\rm rev}, V$             | 0 |  |  |  |  |

| <i>I</i> <sub>rev</sub> , mA | 0 |  |  |  |  |

**11.4.3. Research of a dynistor.** Experimental study of the dynistor is carried out according to the circuit, which is based on Fig. 11.1, c, d, in this order.

To read the forward branch of the dynistor CVC  $I_f(U_f)$ . To make this, by increasing the voltage from zero with the help of the potentiometer R1, it is necessary to determine the voltage in open condition  $U_{oc}$  and the current  $I_f$  across the dynistor and enter the results in Table 11.6.

|   | 1 au      |   | 0                    |                        |                   |                           |                        |              |   |   |  |

|---|-----------|---|----------------------|------------------------|-------------------|---------------------------|------------------------|--------------|---|---|--|

|   | $U_f$ , V | 7 | $U_{bo}, \mathrm{V}$ | $U_{latch},\mathrm{V}$ |                   | $U_{f\max}, V$            | $U_{hold}, \mathrm{V}$ | $U_{rev}, V$ |   | r |  |

| 0 |           |   |                      |                        |                   |                           |                        |              | 0 |   |  |

|   | $I_f, m/$ | ł | Ibo, mA Ilatch, mA   |                        | $I_{f \max}$ , mA | $I_{hold}$ , mA $I_{rev}$ |                        | w, mA        | ł |   |  |

| 0 |           |   |                      |                        |                   |                           |                        |              | 0 |   |  |

Table 11.6

Then, by returning to the zero voltage value and changing it from zero to  $U_f$ , read the three points of the characteristic and enter this data in the same table. To fix the values of the voltage  $U_f$  and current  $I_f$  in the "On-state" of the dynistor and then read three more points, raising the current to the maximum possible value for this open max. By reducing the current from the maximum value, determine the holding current  $I_{hold}$  and the corresponding holding voltage  $U_{hold}$ . Make these measurements in Table 11.6.

Measure the reverse of the CVC branch from  $I_{rev}$  ( $U_{rev}$ ), changing the voltage from zero to the maximum possible value (three points is enough). The results of the measurements are also given in Table 11.6. A sample of the CVC of a dynistor is shown in Fig. 11.9.

#### **11.5.** Processing the results of the experiment

According to the data contained in the Table 11.4, 11.5, and 11.6, to draw the CVC of a direct diode, a Zzener diode, and a dynistor.

Using these characteristics to calculate the static resistances of a rectifier diode, a Zener diode, and a dynistor at the corresponding sections of the CVC:

1) forward resistance at the highest current value

$$R_f = U_{fmax}/I_{fmax};$$

2) reverse resistanceat the highest voltage value

Explain the reason for the difference between the values of the forward and reverse resistances of the devices.

Using the CVC of a Zener diode, calculate the differential resistance on the stabilization part of its CVC

$$R_{\rm dif} = \Delta U_{\rm st} / \Delta I_{\rm st}$$

Calculate the differential resistance of the dynistor in "Off-state" on a branch of the CVC to the **A** point and on the part with unstable operation from the **A** point to the **B** point (Fig. 11.9).

#### **Control Questions**

1. Explain the structure of the p-n junction of the diode.

2. What is the direct and reverse switching on *p*-*n* junction?

3. What physical processes occur in the p-n junction with its direct and reverse switching?

4. What types of breakdowns can occur in the p-n junction, under what conditions and what are their consequences?

5. Explain the phenomenon of capacitance of p-n junction.

6. Explain the design, operation principle and purpose of the rectifier diode, stabilitron and dynistor.

7. To visualize the CVC of the rectifier diode, Zener diode and dynistor and explain their features.

8. What is the static and differential resistance of diodes and dynistors?

### Laboratory work 12

## **RESEARCH OF SINGLE-PHASE RECTIFIERS**

#### **12.1. Purpose of the work**

The purpose of the work is to study the principle of operation and experimental study of one- and two-period rectifiers of single-phase sinusoidal current and smoothing filters.

#### **12.2.** Theoretical provisions

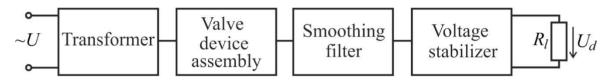

RECTIFIER is a device that converts alternating current into direct current. The rectifier block diagram is shown in Fig. 12.1.

Figure 12.1 – The rectifier block diagram

The transformer regulates the voltage to the required value. The value device assembly (value group) contains elements with one-sided conductivity: rectifier diodes in uncontrolled rectifiers and thyristors in controlled rectifiers. Smoothing filters are designed to reduce the ripple of the rectified voltage. The voltage stabilizer (voltage regulator) keeps the constant voltage across the load resistor  $R_l$ .

There are single-phase and three-phase, controlled and uncontrolled rectifiers.

#### **12.3. Single-phase rectifiers**

#### Schematic diagrams, principle of operation, parameters and characteristics

To rectify a single-phase alternating voltage, three circuits are used:

1) a half-wave circuit;

2) a bridge circuit (Grets circuit);

3) a double half-wave circuit or full-wave circuit (with the lead of the midpoint of transformer or using a central tap transformer).

Half-wave circuit in which the current passes through the valve only for one half-period of the alternating voltage of the source. Double half-wave circuits in which the current passes through the valve group for two half-periods of the alternating voltage of the source.

Consider the ratio of the parameters in the rectifiers under the following assumptions:

1) the leakage inductance of the transformer and the resistance of its windings are equal to zero;

2) the resistance of the valve in the forward direction is equal to zero, and in the opposite direction it is equal to infinity.

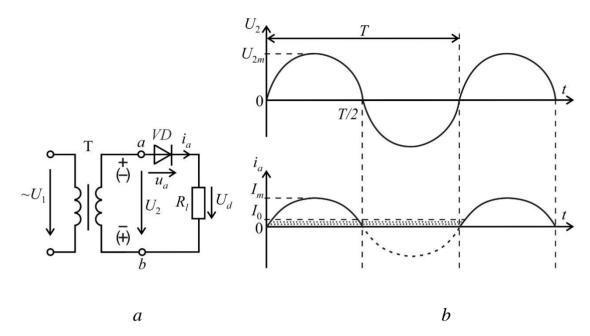

**12.3.1.** A single-phase half-wave rectifier. Time diagrams of voltages and currents. The electric circuit of the rectifier and its time diagrams are shown in Fig. 12.2, *a*, *b*.

Figure 12.2 – The schematic diagram of a single-phase half-wave rectifier (a) and its time diagrams (b)

Define the constant component of the rectified current

$$I_0 T = \int_0^{T/2} i_2 dt$$

Since,  $i_2 = I_m \sin \omega t$  then

$$I_0 T = \int_0^{T/2} I_m \sin \omega t dt = -I_m \frac{\cos \omega t}{\omega} \Big|_0^{T/2} = 2 \frac{I_m}{\omega}$$

$$I_0 = 2 \frac{I_m}{\omega T}.$$

But since  $\omega = \frac{2\pi}{T}$ , i.e.  $\omega T = 2\pi$ , then

$$I_0 = 2\frac{I_m}{\omega T} = \frac{2I_m}{2\pi} = \frac{I_m}{\pi}$$

or  $I_0 = \frac{I_m}{\pi} \approx 0.318I_m$ .

The constant component of the voltage, expressed in terms of the maximum value

$$U_0 = I_0 R_l = \frac{I_m}{\pi} R_l = \frac{U_m}{\pi} = 0.318 U_m$$

The constant component of the voltage, expressed in terms of the actual value (root-mean-square or RMS value)

$$U_0 = \frac{U_m}{\pi} = \frac{\sqrt{2U}}{\pi} \approx 0.45U$$

Thus, in this circuit, the maximum voltage across the diode  $U_m = U_{rev} = \pi U_0 = 3,14U_0,$

the voltage across the diode is three times higher than on the load. The average value of the diode current in this circuit  $I_{av} = I_0$ .

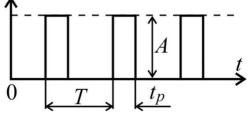

The ripple value of the rectified voltage is characterized by the ripple factor

$$K_r = \frac{U_{1m}}{U_0} \,,$$

where  $U_{1m}$  is the amplitude (peak value) of the variable component of the voltage, changing with the pulse repetition rate, i.e. amplitude of the first harmonic.

For a half-wave circuit

$$U_{1m} = \frac{U_{2m}}{2} = \frac{\pi U_0}{2} = 1,57 \cdot U_0$$

, and  $K_r = 1,57$ .

The disadvantages of the circuit:

1) a large value of the ripple coefficient;

2) the voltage across the load is almost 3 times less than on the diode;

3) the constant component of the rectified current is much less than the current in the secondary winding of the transformer, which leads to its insufficient current use.

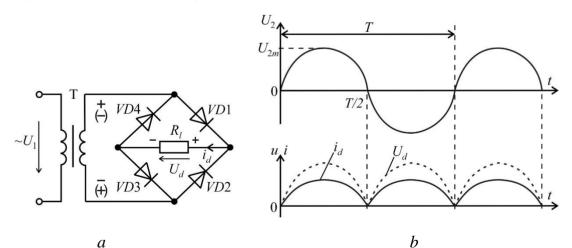

**12.3.2.** A bridge circuit (Grets circuit). The circuit of the rectifier and the time diagrams are shown in Fig. 12.3 *a*, *b*.

Figure 12.3 – The schematic diagram of a single-phase dridge rectifier (a) and its time diagrams (b)

$I_0$  is 2 times greater than in a half-wave circuit. Therefore, it is:

$$U_0 = I_0 R_l = 2 \frac{I_m}{\pi} \approx 0.636 I_m$$

$$U_0 = I_0 R_l = 2 \frac{I_m}{\pi} R_l = \frac{2 \cdot U_m}{\pi} = 0.636 U_m$$

$$U_0 = 2 \frac{U_m}{\pi} = \frac{\sqrt{2} \cdot 2 \cdot U}{\pi} \approx 0.9 U;$$

$$K_l = 0.67$$

The frequency of the rectified current is 2 times higher than that of the network.

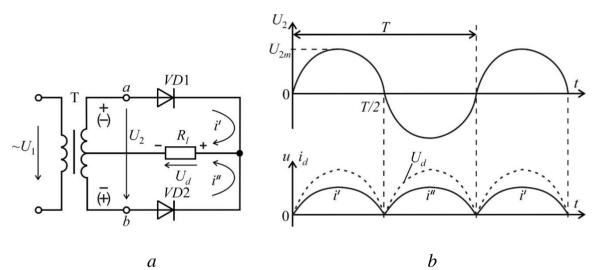

12.3.3. A double half-wave circuit with a midpoint output of a transformer. The circuit of the rectifier and time diagrams are shown in Fig. 12.4, a, b.

Figure 12.4 – The schematic diagram of a double half-wave rectifier (*a*) and its time diagrams (*b*)

This is actually a combination of two half-wave rectifiers connected to the load resistor  $R_l$  in different phases.

The ratio of the parameters in this circuit are the same as in the bridge circuit.

Advantages of the double half-wave rectifiers over the half-wave rectifiers:

The average value of the rectified current and voltage is 2 times greater, and the ripple is less. But double half-wave rectifiers have a more complex design and cost.

Comparison of the double half-wave circuits:

1) the bridge circuit is structurally simpler, its dimensions, weight and cost are lower than the transformer circuit;

2) the maximum reverse voltage on the closed diodes in the bridge circuit is 2 times less (each of the two diodes accounts for half the voltage);

3) but in the bridge circuit, 2 times more diodes are needed.

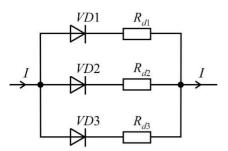

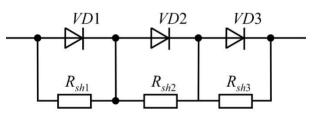

When rectifying the currents  $I > I_{frmax}$  for one diode, in parallel, diodes of the same type with additional resistances are included.

The values of the currents are determined by the resistance in the forward direction. But the resistance of the diodes in the forward directions  $R_f$  even for the same type of diodes are different. To equalize the currents of the diodes, additional resistances are sequentially included. Moreover,  $R_d$  is 5...10 times more than  $R_f$  (Fig. 12.5).

When rectifying a voltage exceeding the maximum allowable for the diode  $U_{rev.max}$ , a serial connection of diodes shunted by resistors are used. In this case, the

Figure 12.5

reverse voltage across the diodes is distributed in accordance with their inverse resistances  $R_d$ . To align the reverse voltages parallel to the diodes, we can include shunt resistors  $R_{sh}$ , the value of which is equal to  $R_{sh} = (0,1...0,2) R_d$  (Fig. 12.6).

Figure 12.6

| Table 12.1 – Parameters | of uncontrollable | e rectifiers with a | resistive load |

|-------------------------|-------------------|---------------------|----------------|

|                         |                   |                     |                |

| Type of a rectifier                        | $U_0$                     | $K_r$ | $U_{ m revmax}$ |

|--------------------------------------------|---------------------------|-------|-----------------|

|                                            |                           |       |                 |

| – half-wave circuit                        | $0,45U_2$                 | 1,57  | 3,14            |

| – double half-wave circuit with a midpoint |                           |       |                 |

| output of a transformer                    | 0,9 <i>U</i> <sub>2</sub> | 0,67  | 3,14            |

|                                            | 0.011                     | 0.67  | 1 57            |

| – bridge circuit                           | $0,9U_2$                  | 0,67  | 1,57            |

## 12.4. Smoothing filters. Schematic diagrams, principle of operation, parameters and characteristics

To reduce the ripple of the rectified voltage, smoothing filters are used. Ripple reduction is estimated by a smoothing <u>coefficient</u>

$$q = \frac{K_r}{K_r'},$$

where  $K_r$  and  $K_r$  are the ripple coefficients before and after the filter.

The main requirements for smoothing filters are the maximum reduction of the high-frequency components of the currents in the load resistance.

The inductive element  $L \Rightarrow X_{Lk} = \omega kL$ , and the capacitive element  $C \Rightarrow X_{Ck} = \frac{1}{\omega kC}$ , where *k* is the harmonic number.

Therefore, the inductor is set in series, and the capacitor is parallel to the load.

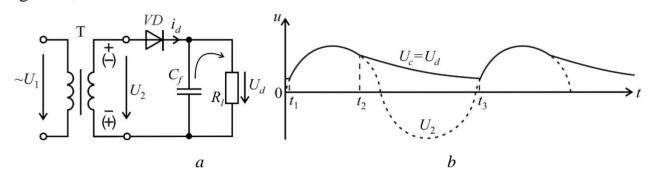

**12.4.1.** A capacitive filter. The schematic diagram of the filter is shown in Fig. 12.7, *a*.

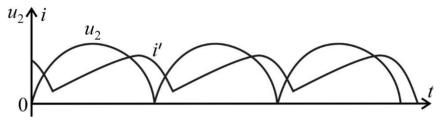

Figure 12.7 – The schematic diagram of the capacitive filter (*a*) and time diagram (*b*)

The capacitor is charged to voltage  $U_2$  when  $U_2 > U_c$  (interval  $t_1 - t_2$ ) as it shown in Fig. 12.7, *b*. During the time interval  $(t_2 - t_3)$ , the voltage  $U_c > U_2$  – the diode is closed, and the capacitor is discharged through the resistor  $R_l$  with a time constant.

From the moment of time  $t_3 U_c < U_2$  – the capacitor is charging, etc. That is, when the diode passes the current, the capacitor is charged, and when the reverse voltage is applied to the diode, the capacitor is discharged to the load  $R_l$ .

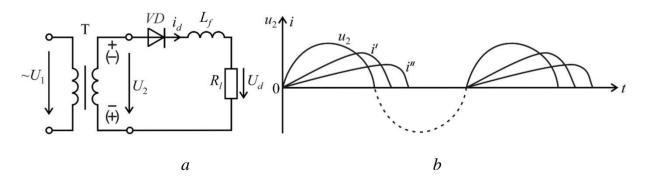

**12.4.2.** An inductive filter. The schematic diagram of the filter is shown in Fig. 12.8, *a*.

Figure 12.8 – The schematic diagram of the inductive filter (a) and time diagram (b)

During the positive half-wave of the voltage  $u_2$ , when the current *i* rises, the inductor  $L_f$  stores energy, and in the negative half-wave, energy is spent on maintaining the current.

The duration of the current  $i_l$  pulses in is determined by the time constant  $\tau = \frac{L_f}{R_l}$ . The larger the inductance of the smoothing inductor (choke)  $L_{f}$ , the more the pulse is pulled and its amplitude decreases due to inductance  $X_L = \omega L_f$ . The average current value also falls.

Typically, an smoothing inductor in half-wave circuits is not used, but used in double half-wave (Fig. 12.9).

Figure 12.9

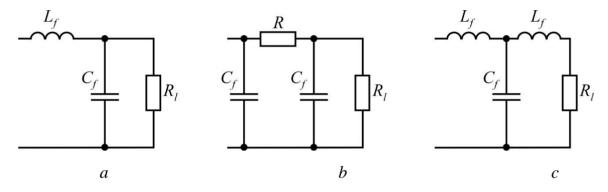

Varieties of smoothing filters (*LC-RC* filters; *L-*, *P-*, *T-* shaped) filters are shown in Figure 12.10, *a*, *b*, *c*.

Figure 12.10

**12.4.3. External characteristics of rectifiers.** The load resistance  $R_l$  changes during operation, which causes a change in the load current  $I_l$ .

Transformers and valves (diodes) have certain values  $R_{tr}$  and  $R_f$  of resistances. At these resistances, the voltage drops from the current  $I_l$ , resulting in a change in the load voltage  $U_l$ .

External characteristic of the rectifier  $U_l(I_l)$

$$U_{l}(I_{l}) = U_{nl} - (R_{f} + R_{tr})I_{l} = U_{nl} - R_{f}I_{l} - R_{tr}I_{l},$$

where  $U_{nl}$  is the rectified voltage at  $I_l = 0$ ;

$R_f I_l$  - the average value of the voltage drop across the diode resistance in the forward

direction;

$R_{tr}I_l$  – the average value of the voltage drop across the resistance of the secondary winding of the transformer.

*The external characteristic* defines the boundaries of the change in the load current at which the rectified voltage does not decrease below the permissible value.

1 - a rectifier without a filter (characteristic is non-linear due to  $R_f$ );

2 - a rectifier with a capacitive filter;

In the no-load mode ( $I_l = 0$ ), the rectified voltage is equal to the amplitude value  $U_{mnl}$ , and without a filter, to the average value.

For a half-wave rectifier  $-U_{lnl} = \frac{U_m}{\pi} = 0.318U_m;$

For a double half-wave rectifier  $-U_{lnl} = 2\frac{U_m}{\pi} = 0,636U_m$ .

With an increase in the load current, curve 2 drops more sharply, since the drop also occurs due to a faster discharge of the capacitor to a lower resistance, which reduces the voltage on the load.

3 – rectifier with a *L*-shaped *RC* filter. An additional decrease in voltage is caused by a voltage drop across the series-connected resistor  $R_{f}$ .

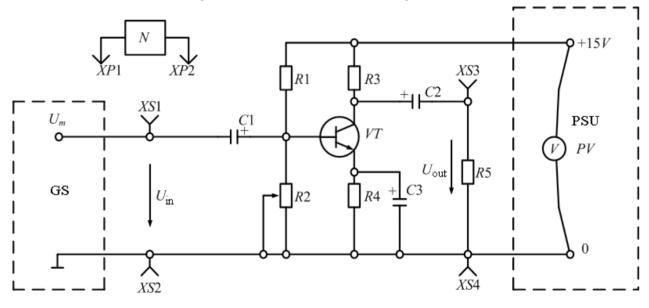

#### 12.5. Object of study

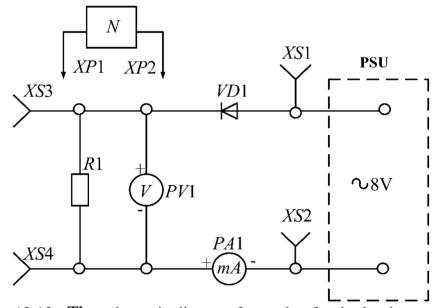

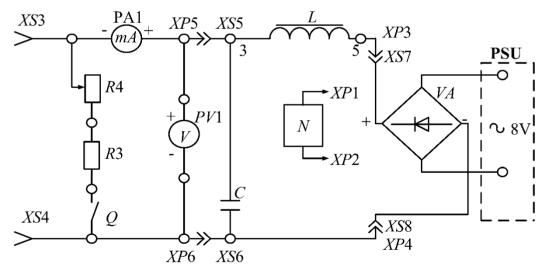

**12.5.1**. In Fig. 12.12 shows the schematic diagram of studies of a single-phase half-wave rectifier, which includes a rectifier diode VD1 and a load resistor R1. The circuit is connected to the terminals of the sinusoidal current source "~ 8V" of the bench power supply unit (**PSU**).

Figure 12.12– The schematic diagram for study of a single-phase half-wave rectifier

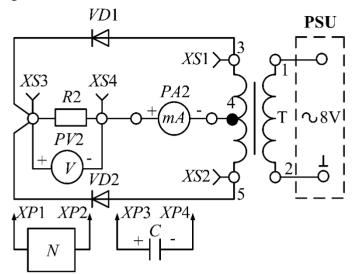

**12.5.2.** The three-point schematic diagram for conducting experimental studies of a single-phase double half-waved rectifier is shown in Fig. 12.13. The circuit is

assembled on the basis of transformer T and includes rectifier diodes VD1 and VD2 and resistor *R*2. The sinusoidal voltage to the circuit is supplied from the terminals " $U_m$ " and " $\perp$ " of the generator signal panel (**GSP**).

**12.5.3.** The schematic diagram for carrying out experimental studies of a single-phase bridge double half-wave rectifier is shown in Fig. 12.14.

The rectifier unit VA includes a four-diode bridge circuit and has four terminals: inputs that connect to a  $\sim 8V$  sine wave power supply unit and outputs (+ and -).

A choke (smoothing inductor) L and capacitor C create a smoothing LC-filter and resistors R3 and R4 activate the rectifier's active

Figure 12.13 – The schematic diagram for study of a single-phase double half-wave rectifier with the lead of the midpoint of transformer

load. One of the windings of the transformer T is used as a choke.

**12.5.4.** DC and voltage are measured respectively by milliammeters *PA*1, *PA*2 and voltmeters *PV*1, *PV*2. Using the N oscilloscope, in all circuits, the voltage form to the rectifier (sockets XS1, XS2) and after it (sockets XS3, XS4) is controlled.

Figure 12.14 – A schematic diagram for study of a single-phase bridge double half-wave rectifier (Grets circuit)

The parameters of the elements included in the diagrams are given in Table 12.2 and Table 12.3.

| Table                 | 12.2                        |                    |             |            |                      |              |

|-----------------------|-----------------------------|--------------------|-------------|------------|----------------------|--------------|

| Diodes<br>VD1, VD2    | The<br>rectifyer<br>unit VA | Constant resistors |             |            | Variable<br>resistor | Capacitor    |

| КД209А                | КЦ405Б                      | <i>R</i> 1         | <i>R</i> 2  | <i>R</i> 3 | <i>R</i> 4           | С            |

| $I_0 = 0,1 \text{ A}$ | $I_0 = 0,1 \text{ A}$       | 470<br>Ohm         | 1,5<br>kOhm | 100<br>Ohm | 470 Ohm              | 10 and 50 µF |

Table 12.3

| Oscilloscope | Milliammeter |      | Voltmeter |     | Switch | Transformer | Choke         |  |

|--------------|--------------|------|-----------|-----|--------|-------------|---------------|--|

| N            | PA1          | PA2  | PV1       | PV2 | Q      | Т           | L             |  |

| C1-67        | 50 mA        | 5 mA | 15 V      | 5 V | MT1    | _           | T, clamps 3,5 |  |

#### **12.6.** The order of the experiment execution

**12.6.1.** Assemble the circuit according to Fig. 12.12 of the elements, the parameters of which are given in Table 12.2 and Table 12.3 for the study of a single-phase half-wave rectifier.

Turn on the "Network On" toggle switch on the PSU. Measure current and voltage and record voltage waveforms at the input and output of the rectifier. Disable network switch to "Network Off".

Turn on the "Network On" toggle switch on the PSU. Measure current and voltage and record voltage waveforms at the input and output of the rectifier. Connect the 10 and 50  $\mu$ F capacitors in parallel to the load resistor and again read the voltage waveforms across the load resistor. Disable the "Network On" switch.

12.6.2. Mount the cicuit according to Fig. 12.13 of the elements, the parameters of which are given in Table 12.2 and 12.3 for the study of the double half-wave rectifier with a midpoint output of a transformer. Set the waveform selector knob to the position "~ sine". Turn on the **GSP** switch and set the maximum signal voltage  $U_m/V$  with the knobs. Measure current and voltage and draw voltage waveforms at the input and output of the rectifier. Connect the 10 and 50  $\mu$ F capacitors in parallel to the load resistor and again read the voltage waveforms across the load resistor. Disable the "**GSP**-on" toggle switch.

**12.6.3.** Mount the diagram according to Fig. 12.14 for the study of a double half-wave bridge rectifier of the elements, the parameters of which are given in Table 12.2 and 12.3.

Turn on the "Network On" switch on the PSU and draw the voltage waveforms of the rectifier output if there is an *LC*- filter.

Read the external characteristic  $U_0$  ( $I_0$ ) of the filter rectifier. To do this, it is necessary to start from no-load mode, i.e. turn off the switch Q and measure the voltage  $U_0$ . Then turn it on and change the resistance of the resistor R4 from high to low. Record the measured values of voltage  $U_0$  and current  $I_0$  in Table 12.4. Disable the "Network On" toggle switch.

Table 12.4

| $U_0, \mathrm{V}$ |   |  |  |  |

|-------------------|---|--|--|--|

| $I_0$ , mA        | 0 |  |  |  |

Exclude the *LC*-filter from the diagram in Figure 12.14 (part of it between pins XP3, XP4 and sockets XS5, XS6) and insert pins XP5, XP6 into sockets XS7, XS8. Turn on the Network On toggle switch and repeat the experiments, i.e., draw the oscillation-diagrams of the rectifier output and read its external characteristic. Write the measured values of voltage  $U_0$  and current  $I_0$  in Table 12.5.

Disable the "Network On" toggle switch.

Table 12.5

| $U_0, \mathbf{V}$ |   |  |  |  |  |  |  |

|-------------------|---|--|--|--|--|--|--|

| $I_0$ , mA        | 0 |  |  |  |  |  |  |

#### **12.7.** Processing the results of the experiment

1. To draw in one coordinate grid the external characteristics  $U_0$  ( $I_0$ ) of a twoperiod rectifier, both with and without the filter, using the data in Table 12.3 and 12.4, and analyze their differences.

2. Display and compare the waveforms of voltages of one- and two-period rectifiers and explain the reasons for the difference.

3. Display and compare the waveforms of a two-period rectifier without filter and filter, and explain the reasons for the difference.

### **Control Questions**

1. Outline the schematic diagrams and explain the principle of operation of the rectifiers studied.

2. Display the time functions of the input voltage and the rectifier load, as well as any diode.

3. Specify the main electric parameters of the circuits of single-phase rectifiers. Compare different circuits on these parameters.

4. What are the parameters of the diodes for different rectifiers?

5. What is the purpose of filters? What filter in the circuits are used?

6. Explain why is a capacitor switched on in parallel with the load and a choke in series, and why they reduce the voltage ripple across the load?

7. What is the voltage or current ripple ratio?

## **RESEARCH OF A LOW FREQUENCY AMPLIFIER**

#### **13.1. Purpose of the work**

The purpose of the work is to study the principles of amplification of lowfrequency electric signals and experimental study of a common emitter amplifier with a bipolar junction transistor, the read of the gain (amplitude) and amplitude-frequency characteristics (AFC) of this amplifier.

#### **13.2.** Theoretical provisions

An electronic amplifier is a device that provides an increase in the power of electric signals supplied to its input.

The amplifier includes:

1) an amplifying (active) element is a nonlinear element (transistor, electron lamp, etc.);

2) passive elements: resistive, capacitive, oscillatory circuit, etc .;

3) power supply (direct current, less often alternating current).

*The source* of input signals are: microphone, photocell, thermocouple, chemical current source, previous amplifier, etc.

*Load of the amplifier* can be: a resistor, an oscillating circuit, a transformer, an electric motor, a speaker, etc.

The purpose of the amplifier element is to convert the electric energy of the power source into the energy of amplified signals.

The simplest amplifier contains one active element with passive elements attached to it, and it is called an *amplifier stage*.

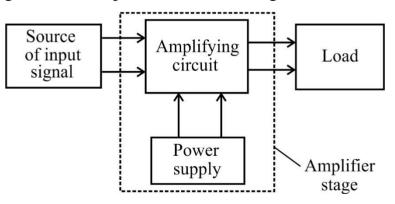

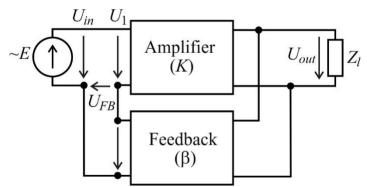

**13.2.1. The functional block diagram of the amplifier stage.** The block diagram of an amplifier is shown in Fig. 13.1.

Figure 13.1 – The functional block diagram of an amplifier

The amplification process is to convert the energy of the power source into the energy of the output signal.

The input signal is a function of the input signal, and the power of the output signal due to the energy of the power source is much greater than the power of the input signal.

## 13.2.2. Amplifier classification.

*By the nature of the amplified signals:*

1) harmonic signal amplifiers; 2) pulse amplifiers.

By appointment:

3) voltage amplifiers; 4) current amplifiers; 5) power amplifiers. *By the nature of the amplifying elements:*

6) transistor amplifiers (with bipolar junction transistors or field effect transistors);

7) tube amplifiers (electronic tubes); 8) magnetic amplifiers, etc.

According to the frequency range of electric signals:

9) amplifiers of low frequency; from tens of Hz to tens of kHz.

10) DC amplifiers; more precisely, amplifiers of slowly changing signals: from 0 Hz to tens and hundreds of kHz.

11) selective or selective amplifiers - amplifying signals in a very narrow frequency band. They are characterized by a small ratio of the upper to lower frequencies  $f_h/f_l < 1,1$ .

12) broadband amplifiers amplifying a very wide frequency band (from a few kHz to several MHz).

According to the type of interstage connections:

13) amplifiers with galvanic coupling;

14) amplifiers with resistive-capacitive coupling;

15) transformer coupled amplifiers;

16) amplifiers with communication through an oscillatory circuit.

**13.2.3. Amplifier main features.** *Gain* is the ratio of the signal at the output to the signal at the input of the amplifier.

We can distinguish between gains: voltage gain  $\left| K_U = \frac{U_{out}}{U_{in}} \right|$ ;

current gain  $K_I = \frac{I_{out}}{I_{in}};$ power gain  $K_P = \frac{P_{out}}{P_{in}} = \frac{U_{out}}{U_{in}} \frac{I_{out}}{I_{in}} = K_U K_I.$

These are dimensionless coefficients. There are very large values and this is inconvenient. Therefore, gain factors are used in logarithmic units – decibels (dB).

The relationship between dimensional and dimensionless coefficients is as follows:

$$K_{P,\mathrm{dB}} = 10 \lg K_P$$

The values of the coefficients  $K_U$  or just K are tens ... hundreds. Sometimes this is not enough. Then a series connection of amplification stages is used.

Since

$$P \sim I^2$$

or  $U^2$ , then  $K_{U,dB} = 20 \lg K_U$

$K_{I,dB} = 20 \lg K_I$

$K_U = 10^{\frac{K_U,dB}{20}}$ .

Reverse transition

If  $K_U$ ,  $_{dB} = 1$  dB, then  $K_U = 10^{1/20} = 1,12$ , i.e. gain of 12%.

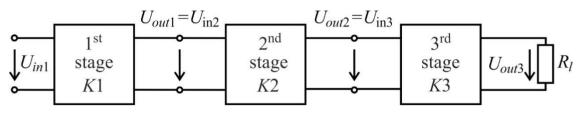

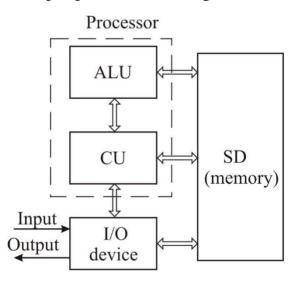

The block diagram of a multistage amplifier is shown in Fig. 13.2.

Figure 13.2 – Multi-stage amplifier

Total gain

$$K = K_1 \cdot K_2 \cdot K_3$$

or  $K = \frac{U_{out3}}{U_{in1}} = \prod_{i=1}^n K_i$

Indeed  $K = \frac{U_{out1}}{U_{in1}} \cdot \frac{U_{out2}}{U_{in2}} \cdot \frac{U_{out3}}{U_{in3}} = \frac{U_{out3}}{U_{in1}}$ ,

because  $U_{out1} = U_{in2}$ ;  $U_{out2} = U_{in3}$ .

For dimensional coefficients

$$K_{\rm dB} = K_{1,\rm dB} + K_{2,\rm dB} + K_{3,\rm dB} = \sum_{i=1}^{n} K_{i,\rm dB}$$

Output power. With an active load, the output power of the amplifier

$$P_{out} = \frac{U_{out}^2}{R_l} = \frac{U_{mout}^2}{2R_l}$$

This is the net power developed by the amplifier in the load resistance. Its increase is limited by distortions due to the nonlinearity of the characteristics of the amplifying elements at large signal amplitudes.

The power at which the distortion does not exceed the allowable value is called the rated output power.

3. *Efficiency*

$$\eta = \frac{P_{out}}{P_0} 100\%$$

where  $P_0$  is the power consumed by the amplifier from all power sources.

4. *Rated input voltage* – sensitivity. This is the voltage that must be brought to the input of the amplifier in order to obtain a given power output. Otherwise, there will be strong signal distortions.

5. The range of amplified frequencies or bandwidth - that region of frequencies in which the gain does not change more than is allowed by the technical conditions.

The expansion of the bandwidth leads to an increase in cost and complexity of the equipment.

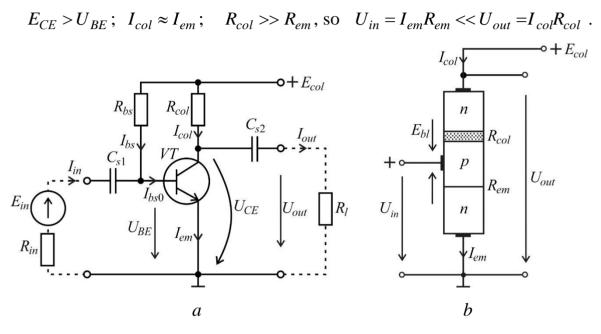

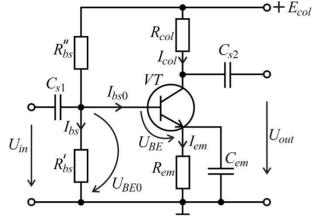

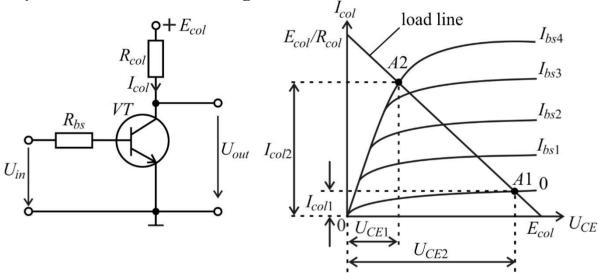

13.2.4. A low frequency common emitter amplifier on a bipolar junction transistor. The transistor VT is *n-p-n* type in Fig.13.3. The polarity of the power supply  $E_{col}$  depends on this. Its value is usually taken 10 ... 15 V.

Figure 13.3 - A schematic diagram of a low frequency amplifier (*a*) and the structure of a *n*-*p*-*n* bipolar junction transistor (*b*)

The input signal arrives at the base and changes its potential relative to the grounded emitter. This leads to a change in the base current, and, consequently, to a change in the collector current and the voltage at the load resistance  $R_{col}$ .

The separation capacitor  $C_{s1}$  serves to prevent the DC component of the base current from flowing through the input signal source (without  $C_{s1}$ , the source will heat up and the transistor will change its operation mode).

Using a capacitor  $C_{s2}$ , an alternating voltage component  $U_{CE}$  is supplied to the output of the cascade, which varies according to the law of the input signal, but significantly exceeds it in magnitude.

The resistor  $R_b$  provides the choice of the initial operation point on the characteristics of the transistor and determines the mode of operation of the cascade of direct current.

For the collector circuit according to Kirchhoff's voltage law

$$E_{col} = U_{CE} + I_{col}R_{col}$$

*I* - *U* characteristic of  $R_{col}$ :  $I_{col}(U_{CE})$  – linear, *I* - *U* characteristic of *VT*:  $I_{col}(U_{CE})$  – non-linear. We build a load line  $U_{CE} = E_{col} - I_{col}R_{col}$  for the resistor

We can build on two points:

1)

$$I_{col} = 0; \implies U_{CE} = E_{col}; 2) U_{CE} = 0 \Longrightarrow I_{col} = \frac{E_{col}}{R_{col}}.$$

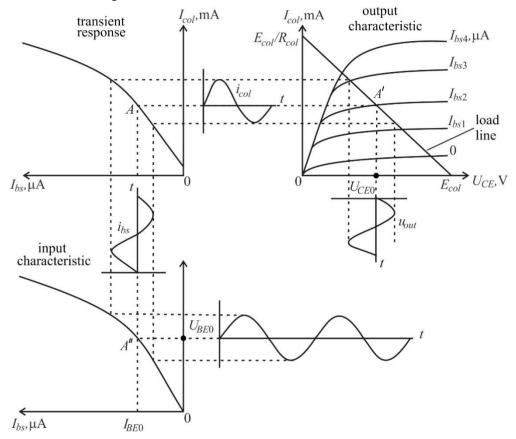

For this and base currents  $I_b$ , you can find the current  $I_{col}$  and voltage  $U_{CE}$  (along the intersection of the curves). Fig. 13.4 shows the input and output characteristics of a bipolar junction transistor.

Using the resistor  $R_b$ , it is possible to obtain in the absence of an input signal a current  $I_{BE0}$  and a voltage  $U_{BE0}$  corresponding to the middle of the linear portion of the input characteristic (point *A*).

Figure 13.4 – Input and output characteristics of a bipolar junction transistor

The resistance of the resistor  $R_b$  is selected from the equation:

$$E_{col} = U_{BE0} + I_{BE0}R_b - \text{at the no-load mode.}$$

$$R_b = \frac{E_{col} - U_{BE0}}{I_{BE0}}$$

The resistor  $R_b$  provides the bias current in the base circuit. Such a shift of the emitter junction is provided by a fixed base current. This is a fixed base current amplifier.

### 13.2.5. Amplifier temperature stabilization.

With increasing temperature, the current  $I_{col}$  increases due to an increase in minority charge carriers, which changes the characteristics of the transistor (the operation point shifts from point A in Fig. 13.4).

In this amplifier, the offset of the emitter junction is provided by a fixed baseemitter voltage, and the amplifier is called a fixed base voltage.

The no-load mode is ensured by the constant bias voltage of the emitter junction using the  $R'_{bs} - R''_{bs}$  divider that is shown in Fig. 13.5.

Voltage  $U_{BE0}$  (direct current in the absence of  $U_{in}$ ):

$$U_{BE0} = I_{bs}R'_{bs} = \frac{E_{col}R_{bs}}{R'_{bs} + R''_{bs}}$$

– an initial shift of the base.

According to Kirchhoff's voltage law:

$$U_{BE} = U_{BE0} - I_{em}R_{em} = \frac{E_{col}R_{bs}}{R_{bs}' + R_{bs}''} - I_{em}R_{em}$$

In the presence of a resistor  $R_{em}$ , an increase in current  $I_{em} = I_{b0} + I_{col}$  due to an increase in temperature leads to an increase in the voltage drop  $I_{em}R_{em}$  on the resistor  $R_{em}$ , which causes a decrease in voltage  $U_{be}$ , and therefore currents  $I_{em}$  and  $I_{col}$ :

$$T \uparrow \Rightarrow I_{col} \uparrow \Rightarrow I_{em} \uparrow \Rightarrow I_{em} R_{em} \uparrow \Rightarrow U_{BE} \downarrow \Rightarrow I_{bs} \downarrow \Rightarrow I_{col} \downarrow$$

Thus, the resistor  $R_{em}$  plays the role of DC feedback.

For alternating current in the presence of  $U_{in}$ : the introduction of  $R_{em}$  creates a voltage drop  $u_{em} = i_{em}R_{em}$ , which reduces the amplified voltage.

Where  $i_{em}$  is the alternating component of the emitter current.

$$U_{BE} = U_{in} - i_{em}R_{em}$$

To attenuate this negative phenomenon,  $C_{em}$  is set in parallel with  $R_{em}$ . The capacitance of  $C_{em}$  is such that  $X_{em} = \frac{1}{\omega C_{em}} << R_{em}$  for all frequencies of the amplifier and then the amplified voltage is almost equal to the input

$$u_{BE} \approx u_{in}$$

,

So that we removed the feedback on alternating current.

Figure 13.5 – Amplifier temperature stabilization

**13.2.6. Self-interference and distortion of the amplifier.** The causes of interference at the amplifier output can be divided into 3 groups:

1) thermal noise;

2) noise of amplifying elements;

3) interference due to ripples in the supply voltage and interference from external electromagnetic fields.

The amount of total noise at the amplifier output should be significantly less than the signal voltage. Typically, the useful signal should exceed the interference level by at least 2 ... 3 times (by 6 ... 10 dB).

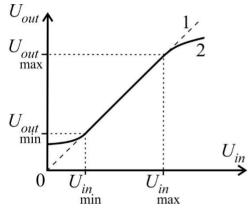

## 13.2.7. Amplitude response (Gain characteristic)

It is dependence  $U_{out}(U_{in})$  shown in Fig. 13.6. At low voltage or in the absence of a signal input, the output voltage is determined by the level of intrinsic noise and the noise of the amplifier at  $U_{in} < U_{in\min}$ .

At high input voltages  $U_{in} > U_{in_{max}}$ , the characteristic is distorted due to overload of the amplifying elements from the input side.

Estimated by the dynamic range of amplitudes in decibels

$$D_{dB} = 20 \lg \frac{U_{in_{\max}}}{U_{in_{\min}}}$$

**13.2.8. Amplifier distortion.** Distortions can be: amplitude or nonlinear, frequency and phase.

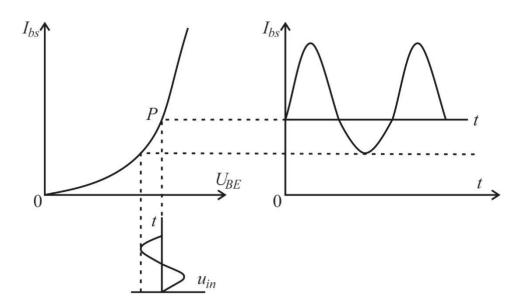

*Nonlinear distortion* is a change in the shape of the curve of amplified oscillations caused by the nonlinear properties of the amplifier circuit (mainly due to the nonlinear characteristics of the transistor).

For example, how do nonlinear distortions appear in the input circuit of an amplifier due to a transistor? It is shown in Fig. 13.7.

Figure 13.6 – Gain characteristic: 1 - ideal; 2 - real

Figure 13.7 – Amplitude distortion

A sinusoidal signal is applied to the input of the amplifier. Getting on a nonlinear section of the input characteristic of the transistor, this signal causes a change in the input current, the shape of which is not sinusoidal. This means that the output current and output voltage change their shape.

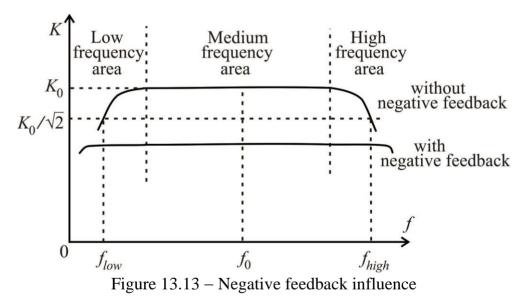

*Frequency distortion* is caused by a change in the magnitude of the gain at different frequencies. Reason is the presence of reactive elements in the amplifier (capacitors, inductors, mounting capacities, etc.).

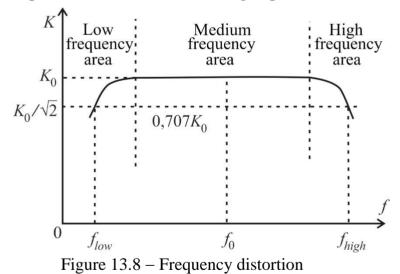

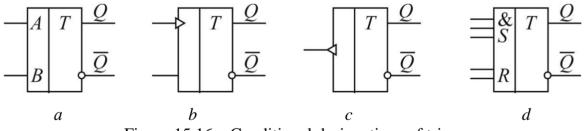

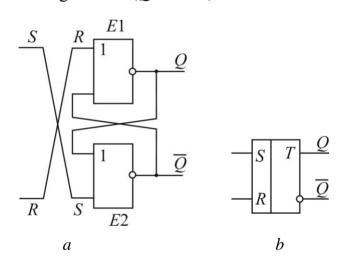

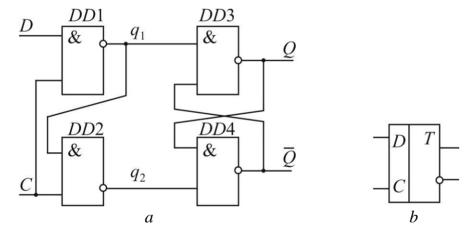

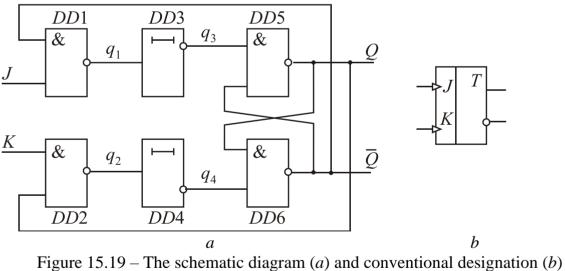

Frequency distortion is estimated by the amplitudefrequency characteristic K(f) or  $U_{out}(f)$ . It is shown in Fig. 13.8, where  $f_0$  is the average transmission frequency;  $f_{low}$ ,  $f_{high}$ are lower and upper boundary frequencies.